- 首頁 >

自旋電子學Spintronics

自旋電子學

電子自旋(spin)指的是電子的角動量,同時也伴隨著磁矩的產生。自旋電子學(spintronics)則是藉由各種手法,來操控電子自旋自由度的科學。自旋電子學具有許多充滿潛力的應用,例如:「稀磁半導體(DMS)」、「磁性隨機存取記憶體 (MRAM)」、「自旋場發射電晶體 (SFET)」、「自旋發光二極體 (Spin LED)」等。自旋的引入,可使現有的這些電子元件產品更加多樣化,並能更穩定、更節能的操作。在上個世紀,人們懂得如何去控制電子的移動,並利用半導體的技術來決定導電度和載子濃度等,創造了資訊時代,在人類歷史上寫下了輝煌的里程碑。而現在人們也普遍的認為,自旋電子學的研究將帶起另一波資訊工業的革命。而因為自旋電子學,我們並可大膽的說,二十世紀是點矽成金的時代,二十一世紀將會是點鐵成金的時代。因此,研究能應用於自旋電子的元件材料,將具有相當的挑戰性及開創性。

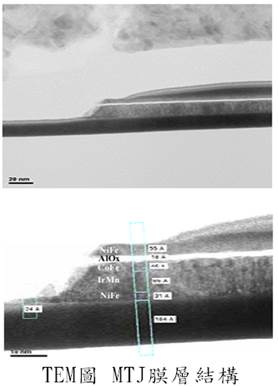

本實驗室這十年來投入了許多研究精力在自旋電子學上,早期的方向主要放在一些磁性材料的基本性質研究,包括鐵磁反鐵磁薄膜的交換異向性(Exchange bias)、半金屬材料(Half-metal)、和稀磁半導體等。近兩年的研究主軸則放在磁性記憶體中的磁性穿隧接合(Magnetic tunnel junction)研究,包括水平式及垂直式MTJ的濺鍍和微小化製程,以及自由層翻轉的電流最佳化。我們同時跨足更先進的跑道記憶體(Racetrack memory)研究,此部分同時從模擬及實驗兩端著手,了解磁區壁裡面的物理,和評估將其元件化的可行性。另外我們也將磁性材料導入薄膜式電感的應用,藉由磁性材料高透磁率的特性,來增加此類被動元件的電感值。

磁性隨機存取記憶體(Magnetic Random Access Memory)

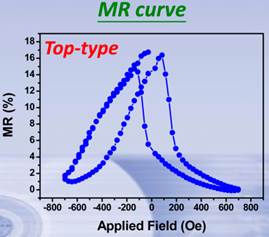

磁記憶體具有速度快、低耗能、高密度、非揮發性,和幾乎可無限次存取的優勢,被預測為是下一世代記憶體的主流,也是自旋電子學最主要的應用領域。磁記憶體的原理是利用穿隧磁阻(Tunneling Magnetoresistance,TMR)效應,來記錄0和1的數位態。磁記憶體的主要結構,是由兩個鐵磁材料中間夾著一層絕緣材料而成的三明治結構來構成,稱為磁性穿隧接合(MTJ)。而此接合的電阻值主要由兩鐵磁層的相對磁化方向來做決定,當兩磁化方向成平行排列時,元件具有較低的電阻值,相反地當兩層的磁化方向是反平行排列時,元件電阻值較高。元件高低電阻態的比例稱為磁阻率(Magnetoresistance Ratio),現今做得最好的元件,其磁阻率高達1000%以上!在寫入時則是固定一層(固定層,Pinned layer)的磁化方向,利用磁場或電流改變另一層(自由層,Free layer)的磁化方向,來改變儲存的值。

磁記憶體的結構

如前所述,磁記憶體的核心部分為一磁性穿隧接合,並且其中兩層鐵磁層分別是固定層和自由層,這種結構又叫自旋閥(spin valve)結構,因為其中一層被固定而另一層可自由翻轉。要做到這種結構有兩種方式,一是選用具有不同矯頑場(coercivity field)不同的兩種磁性材料,或是兩層不同厚度的相同材料,控制兩層翻轉的時機來達到平行態和反平行態,稱為準自旋閥(pseudo spin valve)。另一種則是利用反鐵磁對鐵磁的交換異向性,來達到固定其中一層磁矩的效果,稱為。

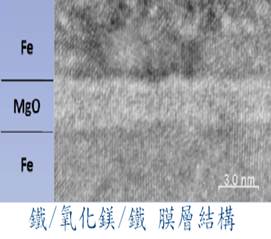

本實驗室在水平式MRAM方面的研究,已成功做出以氧化鋁作為絕緣層材料,搭配鈷鐵硼自由層/固定層的交換異向自旋閥結構,並搭配微小化製程,在室溫時的磁阻率可達25%。而使用離子槍輔助濺鍍的方式,並運用適當的底層(buffer layer)材料,做出鐵/氧化鎂/鐵優選取向的交換異向自旋閥結構,在室溫時達到41%的磁阻率。我們更與日本的東北大學合作,改善製程參數,做出以氧化鎂/鈷鐵硼結構為主的交換異向自旋閥,其室溫的磁阻率高達220%。

如同磁紀錄媒體一樣,磁記憶體的發展勢必從水平異向性的材料走向垂直磁異向性的材料為主。因垂直式材料具有高的熱穩定性,又受去磁場影響小,可以大幅降低元件尺寸,並且不像水平式材料有翻轉過程中,容易遇到漩渦狀磁區(vortex domain)產生,導致翻轉行為不可逆的缺點,為現今磁記憶體研究發展的主流。本實驗室以先前在磁記憶媒體中建立好的多種垂直材料為基礎,成功以鐵鉑合金及鈷鉑多層膜兩種不同矯頑磁力的垂直材料,搭配氧化鎂的絕緣層堆疊出垂直的準自旋閥結構,從磁性質上已可明顯看出兩層平行與反平行的不同排列方式。

電致磁化翻轉(Current Induced Magnetization Switching)

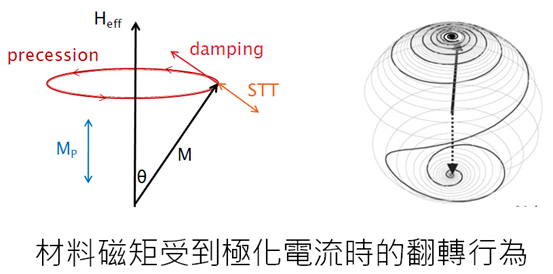

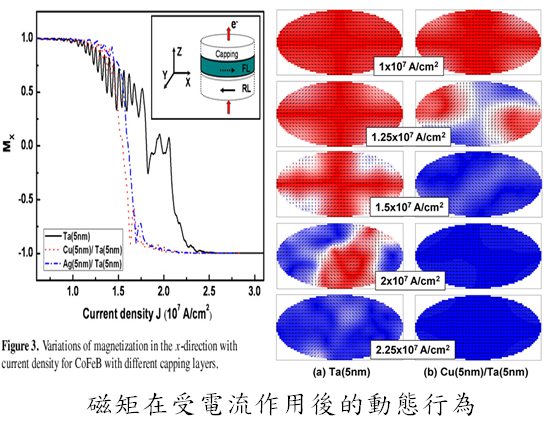

在較早的磁記憶體中,是使用電路中電流產生的磁場來對自由層做翻轉的動作,線路設計較為複雜,且所需要的電流較高、較不利操作。1996年Slonczewski和Berger兩人發現了自旋傳輸效應,可以利用極化電流來翻轉磁矩,此發現簡化了磁記憶體線路設計,也大幅提升了讀寫時的可靠度,使磁記憶體往真實應用又邁進了一大步,此種磁記憶體稱自旋傳輸記憶體(Spin-torque transfer RAM,STT-RAM)。然而磁矩在受電流作用後的行為並不單純,而是一動態翻轉的行為,並且目前欲使磁矩完成翻轉的電流密度過高,比起所搭配的CMOS能提供的電流約大了兩個數量級。因此若真要有效將STT的效應元件化,首要之務便是要降低翻轉電流,目前仍有許多待進步的空間。

磁矩在受電流作用後的動態行為,主要由一動態的磁性參數-阻尼常數(damping constant)來做決定,因此若能夠控制阻尼常數的大小,便能夠去有效降低使磁矩翻轉的臨界電流值,達到元件操作的需求。本實驗室在動態磁性質的研究上,建立了分析鐵磁共振(Ferromagnetic resonance,FMR)圖譜的技術,可以量測得到材料的阻尼常數,並進而去改變它,得到一個較佳的數值。在我們的研究中,藉由改變不同的自由層成份、改變覆蓋層(capping layer)及搭配各種後退火(post-annealing)的製程,我們可以降低材料一半的本質(intrinsic)阻尼常數。同時我們也發現,在製程過程中的副產物常會使自由層材料的異質(extrinsic)阻尼常數大幅增加,有鑒於此我們做了適當的製程改進,異質阻尼常數可以被有效的抑制,得到一個更低的整體阻尼常數值。

磁區壁(Domain Wall)

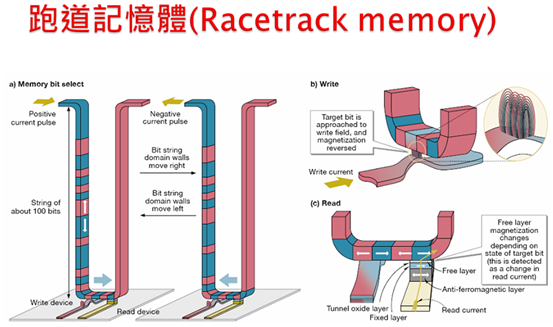

磁區(Magnetic domain)是磁性材料中磁化方向相同的小單位所組成的小區域,而磁區壁是不同磁區的交界線,在塊材或薄膜的磁性材料中,常會形成許多的磁區以降低磁性材料的總能量。IBM公司在2006年提出在次微米級磁性導線上,利用人工的凹痕建立固定大小的磁區作為磁紀錄的單元,並利用電流推動磁區壁移動的效應,來達到更高密度、更高讀寫速度的新一代磁記憶體,稱為跑道記憶體(Racetrack memory)。此為首先應用磁區壁在元件上的想法,並且引發了全世界對於磁區壁物理及工程研究的熱潮。

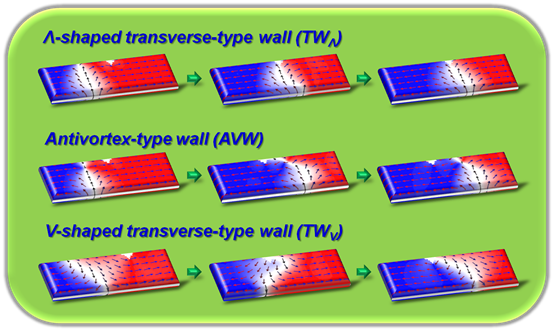

本實驗室利用OOMMF(Object-Oriented Micromagnetic Framework)微磁學模擬探討電流驅動磁區壁穿過凹痕的行為模式。在超過Walker Breakdown的電流密度之後,磁區壁移動時會週期改變磁區壁的型態,不同的磁區壁型態儲存不同的能量,當磁區壁經過刻痕時,儲存的能量會幫助磁區壁脫離刻痕,因此當磁區壁儲存的能量不足時就容易被刻痕固定,無法穿越。此研究中提出一個新的觀點,磁區壁本身儲存的能量對於磁區壁脫離能障有很大的關係,在磁區壁元件設計上,提供了一個重要概念。另外我們也建立了電子束微影的製程技術,可以製作出數百奈米寬的磁性奈米線,從實驗上對於磁區壁的運動作更深入的研究。

軟磁薄膜電感

1.薄膜電感簡介:

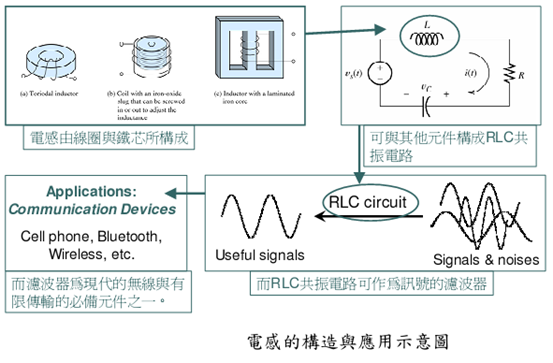

電感(inductors)為電路三種基本元件之一,其基本結構為導線構成的線圈,部份會再加上鐵芯。電感利用電流產生的磁場以及電磁感應,使得頻率高的交流電在電感上會產生高阻抗,並使電感上的電壓和電流相位差為90°。電感可以和其他電路元件搭配做成各式各樣的元件,例如用來選定頻率的濾波器。電感由於由線圈構成,而且其感值(L)和線圈的大小成正比,因此很難縮小並和其他元件行成積體電路。目前所看到的電路,小型電容電阻都可被整合至積體電路中,唯獨電感必須獨立於積體電路之外而做在電路板上或是以其他方式和積體電路封裝成一塊晶片。這也使得電感成為電子元件與產品縮小化的最大阻力之一。

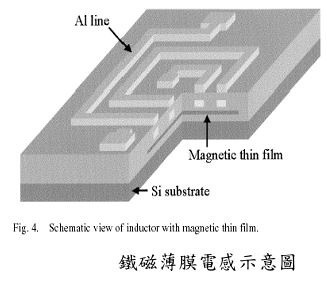

2.鐵磁薄膜電感:

在傳統電感中,我們可以藉著在線圈中插入鐵芯以增強磁場,並大幅提高電感的感值。而在薄膜電感中,我們亦可插入一層鐵磁薄膜來達到類似的效果。若要把鐵磁薄膜應用在薄膜電感上,一般來書有幾個要求:

- 磁導率越高越好

- 薄膜厚度要夠厚,介於數百nm到數um之間,才能有效的增加磁場

- 電阻率越高越好,尤其是在高頻率、高磁導率以及膜很厚的情況下,電阻率要夠高以避免渦電流造成的能量損失

- 在電感的操弄下,鐵磁材料的品質因子要夠大,否則無法使用

3.本實驗室目前成果:

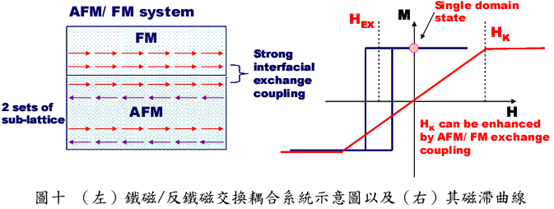

a.整合鐵磁反鐵磁交互耦合多層膜薄膜電感

反鐵磁材料的原子具有磁矩,但磁矩彼此間為反平形排列,此材料磁矩可以和鐵磁材料磁矩彼此耦合,使鐵磁材料只喜好在同一方向,此時鐵磁材料的磁滯曲線會出現不對稱,此即交互耦合(exchange coupling)。而此效應也會使難軸的異向性場Hk提高至100 Oe以上,因此也提高鐵磁共振頻率使得材料能操作在較高頻的環境下。而由於電感所需要較厚的鐵磁層來達到磁場增強的效果,而我們利用多層膜結構來加強交互耦合效應。

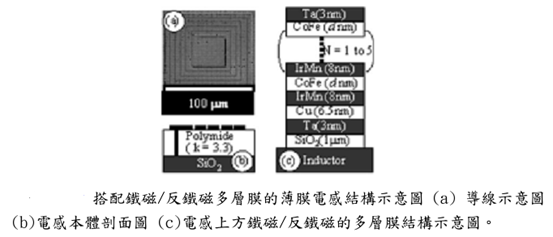

而以下是我們將鐵磁/反鐵磁多層膜和電感整合的成果,最下方是SiO2基版其次為電感本體(即導線線圈),上面為絕緣層和鐵磁/反鐵磁多層膜。

b.CoFeB為基礎的高頻鐵磁薄膜:

鈷鐵硼薄膜具有相當良好的單軸異向性,使得其磁滯曲線和磁導率都接近理論所需,其電阻率也較CoFe高,因此,我們近期以此材料為基礎,研發新的高頻鐵磁薄膜,並進一步研究如何提升其高頻性質。部份研究成果將於近期發表。